# A 100 W SiC MESFET Amplifier for L-band T/R Module of APAR

Wojciech Wojtasiak and Daniel Gryglewski

Abstract—In the paper, a 100W SiC MESFET amplifier design dedicated for a L-band T/R module of APAR is presented. The output power higher than 100 W has been achieved by combining in a balanced configuration two single stages with Cree's 60 W CRF24060 SiC MESFETs. The amplifier design methodology is based on the small-signal model and DC characteristics of SiC MESFET. The model is extracted using the transistor Sparameters at three operating points for On-state, Off-state and normally biased. The measurements and simulations prove usefulness of the proposed design method. The amplifier was excited with pulsed and cw signals for the case temperature ranging from 60°C to 140°C. As a result of the case temperature changes the output power drop was lower than 0.5 dB at the level of 150 W.

Keywords—High power amplifier, SiC, MESFET, T/R Module, APAR.

#### I. INTRODUCTION

IGH-POWER and high-frequency transistor technology is dominated by Silicon (Si) and Gallium-Arsenide (GaAs). However, wide band-gap semiconductors — particularly Silicon Carbide (SiC) and Gallium Nitride (GaN) – have recently gained popularity due to its thermal and electrical properties. Some of the important electrical parameters of the most popular semiconductors are included in Table.I [1],[2].

TABLE I

THE ELECTRICAL PARAMETERS OF THE MOST POPULAR

SEMICONDUCTORS

| Parameters                             | Si              | GaAs         | 4H-SiC             | 2H-GaN           |

|----------------------------------------|-----------------|--------------|--------------------|------------------|

| $E_g[eV] T = 300K$                     | 1.12            | 1.43         | 3.26               | 3.29             |

| $arepsilon_r$                          | 11.9            | 13.6         | 9.7                | 9                |

| $E_B[\times 10^6 V cm^{-1}]^*$         | 0.3             | 0.4          | 3                  | 3.3              |

| $\kappa[W/(cm^{\circ}K)]$              | 1.4             | 0.5          | 4.9                | 1.3              |

| $\mu_n[cm^2/(Vs)]^{**}$                | 1430            | 6000         | 900                | 900              |

| $\mu_p[cm^2/(Vs)]^{**}$                | 450             | 330          | 115                | 300              |

| $v_{sat}[\times 10^7 cm/s]$            | 1               | 2            | 2                  | 2.5              |

| $n_i[cm^{-3}] \text{ T} = 300\text{K}$ | $1.5 \ 10^{10}$ | $2.1 \ 10^6$ | 5 10 <sup>-9</sup> | $1.9 \ 10^{-10}$ |

$<sup>^*</sup>N_D=10^{17}cm^{-3},\,^{**}N_D=10^{16}cm^{-3}$

It is a well-known fact in solid-state physics fundamentals that the semiconductor maintains its properties vs. temperature

This work was supported by the Ministry of Science and Higher Education for the years 2007-2010 as development project.

The authors are with Institute of Radioelectronics, Warsaw University of Technology, Nowowiejska 15/19, 00-665 Warsaw, Poland (e-mails: {W.Wojtasiak, D.Gryglewski}@ire.pw.edu.pl).

as long as its conductivity is only determined by the carrier density coming from ionized dopants and the intrinsic generation is negligible. The intrinsic carrier concentration  $(n_i)$ as well as undesired current leakage depends exponentially on the semiconductor band-gap energy and temperature. For wide band-gap materials such as SiC and GaN, the  $n_i$  density is cir 20 orders of magnitude lower than for Si. Therefore silicon devices operation is limited to junction temperatures less than 300°C, while SiC elements can theoretically achieve the junction or channel temperatures over 800°C. The capability of SiC devices to operate at such high temperatures has been experimentally confirmed for the temperature range up to 600°C [3]. Additionally, SiC has perfect features, such as high electric breakdown field  $(E_B)$  and high thermal conductivity  $(\kappa)$ , allowing for designing of high-voltage and high-power devices. These advantages combined with very low current leakage make it possible to use the SiC devices as switching elements and rectifiers in the power converters. However, employing SiC diodes in AC/DC converters with processed power reaching up to a few hundred watts and conversion frequency lower than 50 kHz operating in the typical temperature range is not advantageous in terms of maximum efficiency. This is due to the high forward voltage (Schottky barrier diode - on the order of 1.5 V, PIN diode and merged PIN Schottky diode — more than 3 V). For RF and microwave power applications the SiC is, in particular, used to manufacture SiC transistors such as MESFETs and SITs (Static Inductance Transistor), and as substrate for GaN HEMT. As shown in Table I the lowfield electrons mobility of the normally doped SiC is relatively low. It is lower than for other "microwave" semiconductors. The low carrier mobility in SiC is, to some extent, balanced by the high carrier saturation velocity coupled with very high breakdown voltage and high thermal conductivity. Because the operating frequency range of the commercially available SiC MESFETs reaches up to a few gigahertzs, the SiC MESFETs are a viable alternative for enhancement-mode GaAs power FETs as well as for GaN HEMT especially in lower microwave bands such as L- and S-band. Commercial availability of microwave SiC MESFETs is still limited, as the dominant manufacturer — Cree Inc. — currently offers only two SiC MESFETs capable of operation at frequencies up to 2.7 GHz. These devices are CRF24010 and CRF24060 and they offer maximum output power level of 10 W and 60 W, respectively. The excellent thermal properties and voltage robustness of SiC enable the SiC devices to be used in special applications such as radar systems, particularly in APAR (Active Phased-Array Radar). The paper presents design and development of a 100 W power amplifier in balanced configuration with two

## 60 W SiC MESFETs for L-band T/R module of APAR.

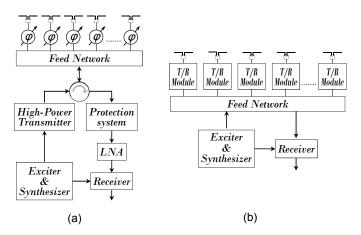

# II. BASIC ACTIVE PHASED-ARRAY FRONT-END ARCHITECTURES

The electronically scanned arrays (ESA) can be met in many configurations, but generally, there are two basic types of phased-array antennas i.e. passive and active, as outlined in Fig.1 [4]. As illustrated in Fig.1a, linear passive array includes a central high-power transmitter and receiver, and uses electronically controlled phase shifters located at the input of each subarray rather than at each single radiating element to provide the desired phase shift for steering the antenna beam. An active array has a distributed architecture designed while taking into consideration the transmitted power generation and low-noise amplification of received signals. The distributed structure idea comes down not only to the distributed amplification on transmit and receive, but also the power dividing/combining at the aperture. To realize this concept, an active array uses Transmit/Receive (T/R) modules located directly behind subarrays or single radiating elements, as shown in Fig.1b. Consequently the central transmitter based on high-power microwave tubes such as magnetron, travelling wave tube (TWT) or klystron, is replaced by distributed solidstate power amplifiers (SSPA) being parts of T/R modules.

Fig. 1. Passive (a) and active (b) phased-array front-end architectures.

The use of solid-state components to manufacture T/R modules allows phased arrays to increase reliability, maintainability, flexibility and added system capability. T/R modules have to fulfill severe climatic conditions and exhibit high structural integrity. Especially, the high power transmitting amplifiers are sensitive to changes in temperature and require efficient and intelligent cooling for maintenance of temperature inside T/R module within the desired range. The above requirements follow not only from the need for protecting the T/R module against overheating, but also limiting amplifier parameters variation during radar pulse. Employing SiC MESFET in the transmitting amplifier design allows significantly reducing the scale of many thermal problems, which is a result of SiC advantages. For example, a cooling system would be made far smaller than in case Si or GaAs devices or even eliminated completely.

### III. T/R MODULE STRUCTURE AND OPERATION

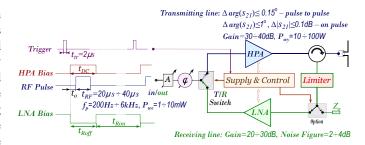

The simplified block diagram of the T/R module structure with approximated values of basic parameters and control scheme is shown in Fig.2 [5].

Fig. 2. T/R module block diagram with typical parameters and control scheme.

As shown in Fig.2, T/R module is composed of a variable attenuator (A), variable phase shifter ( $\phi$ ), switch T/R, multistage transmitting amplifier (HPA), receiving line including low-noise amplifier (LNA) with limiter, common multifunction block for bias, protection and control of active components and interchanging of data as well as circulator placed at the other end. T/R modules operate in half-duplex mode with T/R switch as a duplexer to select transmit and receive functions. A circulator directs signals from antenna into receiving line and prevents high-power amplifier damage and pulling. Since the attenuator and phase shifter are located before the switch, at the input of HPA and the output of LNA, their influence on transmitted power level and noise figure value of the T/R module is relatively insignificant. The amplitude and phase control capability improves performance and, in particular, sensitivity of an active array compared to a passive array, which uses only phase shifters to provide the required phase shift for vertical scanning. The transmitting amplifier is activated by trigger  $(t_{tr})$  of  $\sim 2\mu s$  pulse width. After the RF-pulse  $(t_{RF})$ , the module returns to receive mode  $(t_{Ron})$ . To increase an overall efficiency and reduce thermal effect, the high-power transistors operate in keyed class A or AB. They are biased only during the RF-pulses. It is obvious that the bias duration of transistors must be slightly longer than the RF-pulse width.

# IV. SIC MESFET MODELING

To design a driver and final stage of transmitting amplifier the CRF24010 and CRF24060 SiC MESFET manufactured by Cree Inc. were chosen. Some of the more important parameters such as output power level at 1dB gain compression point  $P_{1dB}$ , small-signal gain  $G_{ss}$ , saturated drain current  $I_{DSAT}$ , breakdown voltage  $V_{DSBR}$ , pinch-off voltage  $V_p$ , maximum channel and case temperature  $T_j$  and  $T_{cop}$ , and recommended operating point of transistors for RF-off coming from the data sheet are given in Table II. In case of CRF24060 transistor, the parameters included in Table II were measured using CRF24060-TB demonstration test fixture at the operating point  $V_{DS}$ =48 V,  $I_{DQ}$ =2 A for f=1.5 GHz [1]. Cree, Inc. has also provided typical S-parameters for both transistors at two operating points i.e.  $V_{DS}$ =48 V,  $I_{D}$ =0.25 A and 0.5 A for CRF24010, and  $V_{DS}$ =48 V,  $I_{D}$ =1 A and 2 A for CRF24060.

| TABLE II                                        |

|-------------------------------------------------|

| THE CRF24010 AND CRF24060 DATA SHEET PARAMETERS |

| $P_{1dB}$ | $G_{ss}$ | $I_{DSAT}$ | $V_{\mathrm{DSBR}}$ | $V_{P}$ | $T_{j}$                 | ClassAB*                          |

|-----------|----------|------------|---------------------|---------|-------------------------|-----------------------------------|

| 12W       | 15 dB    | 1.5A       | 100V                | -10V    | $255^{\circ}\mathrm{C}$ | $I_{\mathrm{DQ}} = 0.5\mathrm{A}$ |

| 60W       | 13dB     | 7.5A       | 100V                | -10V    | 255°C                   | $I_{\mathrm{DQ}} = 1\mathrm{A}$   |

$<sup>*</sup>V_{DSQ} = 48V$

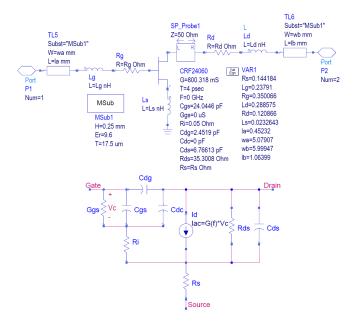

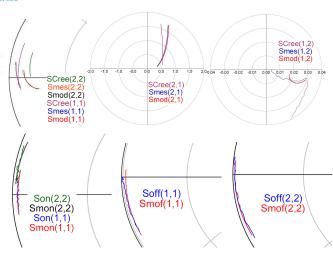

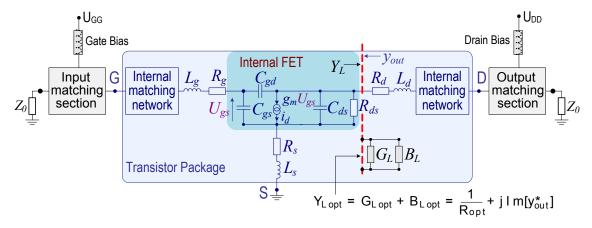

The proposed amplifier design uses the SiC MESFET model, which is needed to synthesize input and output matching sections as well as biasing circuits. This model is based on the small-signal approach for determining of the transistor's equivalent circuit parameters. For this purpose, the S-matrix measurements are performed for three operating points of the transistor: "Off-state" ( $V_{GS}=V_p$ ,  $V_{DS}=V_{DSQ}$ ), "On-state" ( $V_{GS}$ =0 V,  $V_{DS}$ =0 V) and "Nb-state" — normally biased transistor at the predicted working conditions ( $V_{DS}=V_{DSQ}$ ,  $I_D = I_{DQ}$ ). The simulated S-parameters are fitted to the measured ones. To this end S-matrix measured at 3 bias states of the transistor were used as input data for the ADS. Thus, values of equivalent circuit elements of transistor can be found. For example, the CRF24060F SiC MESFET model is presented below. The operating points of transistor for these states were as follows: On-state:  $V_{GS}$ =0 V,  $V_{DS}$ =0 V, Off-state:  $V_{GS}$ =-9.2 V  $V_{DS}$ =48 V and Nb-state:  $V_{DS}$ = 48 V,  $I_{D}$ =3 A. Using the approach a model of CRF24060 SiC MESFET was prepared and its architecture is shown in Fig.3. The model simulations have been compared with transistor measurements and Cree's data sheet for three states from 800 MHz to 3 GHz frequency range, as shown in Fig.4

Fig. 3. CRF24060 SiC MESFET model architecture — external and internal FET.

Fig. 4. CRF24060 model simulations and transistor measurements at the bias points: Nb-state (model — Smod, measurement — Smes, Cree — SCree), On-state (model — Smon, measurement — Son), Off-state (model — Smof, measurement — Soff).

# V. AMPLIFIER DESIGN

The amplifier was designed to achieve more than 100 W output power from 1.2 GHz to 1.4 GHz frequency range. This output power level can be obtained with combining of two 60 W CRF24060 SiC MESFET stages. Due to the advantages such as low input return losses the balanced configuration of amplifier was chosen. At first, however, a single stage needs to be optimized for maximum output power. Therefore the amplifier design could be based on the small-signal model and DC I-V transistor characteristics.

The input matching section of the amplifier is designed using the measured S-matrix of the normally biased transistor. As a result of the finite isolation between the output and input of the transistor  $(s_{12} \neq 0)$ , the optimum load adjusted for maximum output power, affects the input impedance value. The source impedance changes only the imaginary part of the load impedance, because, in this case, the real part is determined from DC I-V transistor characteristics. The structure of both matching sections are optimized for desired values of input return loss, gain and also to fulfill the output admittance condition in the given frequency range. While designing matching and biasing circuits it is also needed to solve the problem of the stability of the amplifier in whole frequency range i.e. within the desired band as well as out of this band. Especially for low frequencies, where microwave transistors usually exhibit conditional stability. Generally, there are two approaches to solving the transistor stability problem. The first is based on introducing losses into the input biasing circuit. It is viable, when the transistor is unstable only for low frequencies and far from the operating band. The second approach consists in removing the transistor instability within or close to the operating frequency range. In such case it is necessary to insert the losses into both the input matching section and the biasing circuit. For high power amplifiers the losses included in the input matching circuit can be difficult to accept due to the limited robustness of SMD resistors. The load admittance is realized with employed elements  $R_d$ ,  $L_d$ ,

Fig. 5. The concept of the proposed amplifier design.

in the plane of  $R_{DS}$  and  $C_{DS}$ , together with the matching circuits inside and outside of the transistor including the drain biasing circuit, as shown in Fig.5.

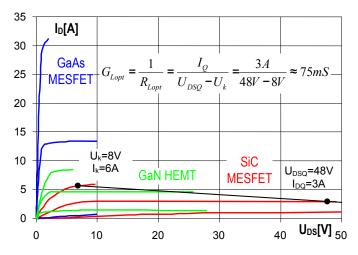

The admittance matching condition for maximum output power was determined at the SP\_Probe1 plane on the model in Fig.3. The real part of load admittance was calculated from DC I-V characteristics as shown in Fig.6. The differences in DC I-V characteristics between GaAs MESFET, GaN HEMT and SiC MESFET of the same output power are also presented in Fig.6. The advantages such as higher drain voltage at low saturated current of SiC MESFET allow achieving high optimum resistance for maximum output power. It makes the output matching section and the biasing circuit easier to manufacture.

Fig. 6. GaAs MESFET, GaN HEMT, SiC MESFET DC characteristics and the formula for calculating of optimum conductance  $G_{Lopt}$ .

At first the imaginary part of load admittance  $B_{Lopt}$  is directly obtained from the S-parameters measured for the Nb-state of transistor. But the  $B_{Lopt}$  value is subject to change with the input matching as a result of the transistor finite isolation. Hence, the synthesis of the input and output matching sections comes down to an iterative process, which stops only when the admittance condition at the SP\_Probe1 plane is fulfilled. The ADS layout of the designed single amplifier is

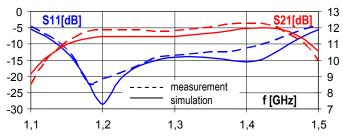

presented in Fig.7. The admittance condition at the SP\_Probe1 plane (L.Y(1,1) to transistor, R.Y(1,1) to load) is presented in Table.III. The small-signal simulations and measurements of single amplifier are shown in Fig.8. As shown in Fig.9,

Fig. 7. The single amplifier layout with CRF24060 SiC MESFET (substrate: RT/Duroid  $\varepsilon_{T}$ =10.2 h=1.27mm, t=35 $\mu$ m).

Fig. 8. The small-signal gain and return loss of single amplifier vs. frequency.

TABLE III

ADMITTANCE CONDITION AT THE SP\_PROBE1 PLANE

| frequency $L.Y(1,1)$ |                | R.Y(1,1)       |

|----------------------|----------------|----------------|

| $1.100~\mathrm{GHz}$ | 0.038 + j0.089 | 0.070 - j0.131 |

| $1.150~\mathrm{GHz}$ | 0.043 + j0.099 | 0.071 - j0.115 |

| $1.200~\mathrm{GHz}$ | 0.049 + j0.105 | 0.075 - j0.104 |

| $1.250~\mathrm{GHz}$ | 0.052 + j0.108 | 0.081 - j0.099 |

| $1.300~\mathrm{GHz}$ | 0.052 + j0.111 | 0.086 - j0.102 |

| $1.350~\mathrm{GHz}$ | 0.050 + j0.117 | 0.085 - j0.111 |

| 1.400 GHz            | 0.049 + j0.127 | 0.075 - j0.120 |

| $1.450~\mathrm{GHz}$ | 0.052 + j0.142 | 0.060 - j0.122 |

| $1.500~\mathrm{GHz}$ | 0.062 + j0.158 | 0.044 - j0.118 |

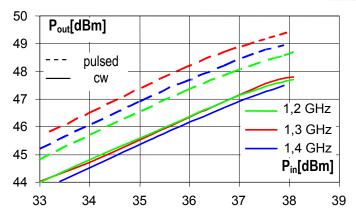

the pulsed and cw power characteristics ( $P_{out} = f(P_{in})$ ) of the single stage measured for a few frequencies from the

Fig. 9. The pulsed and cw  $P_{out} = f(P_{in})$  characteristics of single stage for 1.2 GHz, 1.3 GHz and 1.4 GHz.

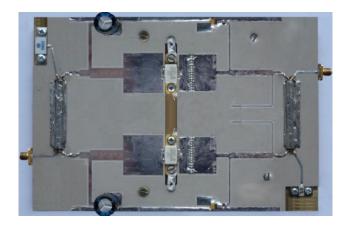

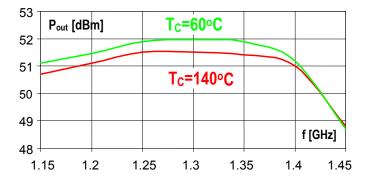

operating band met the design requirements. The view of the balanced amplifier with two CRF24060 SiC MESFETs is shown in Fig.10. The output power level of this amplifier significantly exceeds 100W in the whole frequency band and over a wide temperature range as presented in Fig.11.

Fig. 10. The photo of of the balanced amplifier with CRF24060 SiC MEFSETs.

Fig. 11. The output power vs. frequency (for  $P_{in}=41dBm$ ) of the balanced amplifier with SiC MEFSET for two case temperatures Tc=60°C and 140°C.

# VI. TRANSMITANCE VARIATIONS OF HPA

It was found that temperature fluctuations in an active area of transistor cause transmittance variations of HPAs [7],

[8] within linear or close to linear range. DC supply and AC excitation conditions determine the shape of temperature distribution with ambient temperature  $T_o$  as the initial value. To design HPAs for T/R modules, the electro-thermal (E-T)model of microwave high-power transistors is needed to predict the amplifier behaviour. It allows us to optimize the amplifier structure for chosen parameters such as output power level, gain, and first of all transmittance variations during the RF pulse. The temperature response i.e. transient temperature distribution in an active area of the transistor can be achieved either by the numerical solution of heat conducting equation [7],[8],[9] for defined thermal structure of transistors or using the transient thermal impedance  $Z_{th}$  determined by means of measurement techniques [10]. The view of test system for measurement of thermal impedance curve is shown in Fig.12. The concept of the system consists of the  $\Delta U_{GS}$  measurement

Fig. 12. The test system for thermal characteristics measurements.

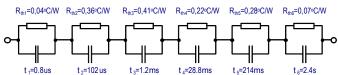

of forward biased gate-source junction during the time of transistor cooling (the second measurement step) [10]. The first measurement step is transistor heating with bias suggested by transistor manufacturer. The method is an evaluation of the similar one described in the MIL-STD-750D standard. The test system was used to extract the structure and parametrs of the lumped thermal model of CRF24060 SiC MESFET, which is shown in Fig.13. The measured transmittance phase

Fig. 13. The lumped thermal model of CRF24060 SiC MESFET.

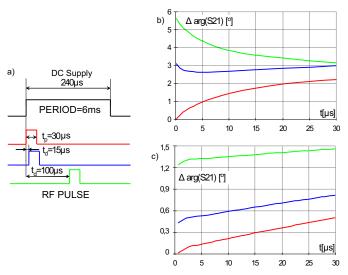

changes of two amplifiers with GaAs and SiC MESFET are presented in Fig.14. The Figure 14 (b) presents results for  $P_{out}=P_{1dB}=10W$  amplifier with GaAs FLL120MK (FUJITSU) and Fig.14 (c) for  $P_{out}=P_{1dB}=60W$  amplifier with CRF24060. The bias time conditions were the same — Figure 14 (a). The transmittance phase changes during RF pulse for SiC MESFET are 5 times smaller for delay time of  $t_d=0$  and they are almost independent of  $t_d$ . Another situation is made for the GaAs transistor. This is due to the thermal time constants, this in case of SiC transistors are 100 times higher than for GaAs ones.

Fig. 14. The DC and RF supply condition under test (a) and transmittance phase changes characteristics of amplifiers with: GaAs, FLL120MK (b) and SiC, CRF24060 (c).

# VII. CONCLUSIONS

The CRF24060 SiC MESFET is used to design the high power amplifier especially for L-band T/R module of APAR. The power SiC MESFETs exhibit a few essential advantages. Particularly, the thermal robustness should be emphasized. Another important feature for designer is high value of optimum resistance for maximum output power compared to other types of microwave transistors such as GaAs FET and GaN HEMT. The performed amplifier measurements fully confirm

the proposed design methodology. The amplifier achieves output power level higher than 100 W both for pulsed and cw excitation from 1.2 GHz to 1.4 GHz frequency range. As a result of the case temperature changes from 60°C to 140°C the output power drop is lower than 0.5 dB. It confirms excellent thermal properties of SiC materials. It was established however that rise in case temperature over 140°C caused damage to the ceramic transistor package. Hence it seems that temperature operating range of power SiC MESFET is limited by the material package properties.

#### REFERENCES

- [1] S. M. Sze, Semiconductors Devices: Physics and Technology, 2nd ed. New York: John Wiley and Sons Inc, 2002.

- [2] R. Clarke, C. Brandt, S. Sriram, R. Siergiej, A. Morse, A. Agarwal, L. Chen, V. Balakrishna, A. Burk, and Northrop Grumman Corp., Pittsburgh, PA, "Recent Advances in High Temperature, High Frequency SiC," in *Proceedings of High-temerature Electronics Materials, Devices* and Sensors Conference, 1998, pp. 18–28.

- [3] D. Parker and D. C. Zimmermann, "Phased Arrays—Part I: Theory and Architectures," *IEEE Transactions on Microwave, Theory and Techniques*, vol. 50, no. 3, pp. 678–687, 2002.

- [4] D. Gryglewski, T. Morawski, E. Sedek, and W. Wojtasiak, "T/R Modules for APAR" *Elektronika*, no. 4, pp. 56–63, 2009

- for APAR," *Elektronika*, no. 4, pp. 56–63, 2009.

[5] W. Wojtasiak and D. Gryglewski, "Temperature-Dependent Modelling of High Power MESFET Using Thermal FDTD Method," in *Microwave* Symposium Digest, 2001 IEEE MTT-S International, vol. 1, 2001, pp. 411–414.

- [6] R. Michnowski and W. Wojtasiak, "The Electro-Thermal Model of High Power LDMOS FET," vol. 1, 6-10 October 2003, pp. 243–246.

- [7] W. Wojtasiak, "The Eectrothermal Modeling of High Power Microware FET and its Applications," *Electronics and Telecommunications Quarterly*, vol. 51, pp. 85–104, 2005.

- terly, vol. 51, pp. 85–104, 2005.

[8] J. L. B. W. (editor), High-Power GaAs FET Amplifiers. Artech House, Inc., 1993.